## PS2 Controller IP Core For On Chip Embedded System Applications

# <sup>1</sup>,V.Navya Sree , <sup>2</sup>,B.R.K Singh

<sup>1,2</sup>.M.Tech Student, Assistant Professor Dept. Of ECE, DVR&DHS MIC College Of Technology, Kanchikacherla, A.P India.

## ABSTRACT

In many case on chip systems are used to reduce the development cycles. Mostly IP (Intellectual property) cores are used for system development. In this paper, the IP core is designed with ALTERA NIOSII soft-core processors as the core and Cyclone III FPGA series as the digital platform, the SOPC technology is used to make the I/O interface controller soft-core such as microprocessors and PS2 keyboard on a chip of FPGA. NIOSII IDE is used to accomplish the software testing of system and the hardware test is completed by ALTERA Cyclone III EP3C16F484C6 FPGA chip experimental platform. The result shows that the functions of this IP core are correct, furthermore it can be reused conveniently in the SOPC system.

KEYWORDS: Intellectual property,

## I. INTRODUCTION

An intellectual property or an IP core is a predesigned module that can be used in other designs IP cores are to hardware design what libraries are to computer programming. An IP (intellectual property) core is a block of logic or data that is used in making a field programmable gate array (FPGA) or application-specific integrated circuit (ASIC) for a product. As essential elements of design reuse, IP cores are part of the growing electronic design automation (EDA) industry trend towards repeated use of previously designed components. Ideally, an IP core should be entirely portable - that is, able to easily be inserted into any vendor technology or design methodology. Universal Asynchronous Receiver/Transmitter (UART s), central processing units (CPU s), Ethernet controllers, and PCI interfaces are all examples of IP cores. IP cores may be licensed to another party or can be owned and used by a single party alone. The term is derived from the licensing of the patent and source code copyright intellectual property rights that subsist in the desig IP cores can be used as building blocks within ASIC chip designs or FPGA logic designs It IP cores in the electronic design industry have had a profound impact on the design of systems on a chip. By licensing a design multiple times, IP core licensor spread the cost of development among multiple chip makers. IP cores for standard processors, interfaces, and internal functions have enabled chip makers to put more of their resources into developing the differentiating features of their chips. As a result, chip makers have developed innovations more quickly.

## II. IP CORES:

IP cores fall into one of three categories: hard cores, firm cores, or soft cores. Hard cores are physical manifestations of the IP design. These are best for plug-and-play applications, and are less portable and flexible than the other two types of cores. Like the hard cores, firm (sometimes called semi-hard) cores also carry placement data but are configurable to various applications. The most flexible of the three, soft cores exist either as a netlist (a list of the logic gate s and associated interconnections making up an integrated circuit) or hardware description language (HDL) code. The IP core can be described as being for chip design what a library is for computer programming or a discrete integrated circuit component is for printed circuit board design. The IP core can be described as being for chip design what a library is for computer programming or a discrete integrated circuit board design.

## A. SOFT CORES:

IP cores are typically offered as synthesizable RTL. Synthesizable cores are delivered in a hardware description language such as Verilog or VERILOG. These are analogous to high level languages such as C in the field of computer programming. IP cores delivered to chip makers as RTL permit chip designers to modify designs (at the functional level), though many IP vendors offer no warranty or support for modified designs.

IP cores are also sometimes offered as generic gate-level net lists. The net list is a boolean-algebra representation of the IP's logical function implemented as generic gates or process specific standard cells. An IP

www.ijceronline.com

core implemented as generic gates is portable to any process technology. A gate-level net list is analogous to an assembly-code listing in the field of computer programming. A net list gives the IP core vendor reasonable protection against reverse engineering.

Both net list and synthesizable cores are called "soft cores", as both allow a synthesis, placement and route (SPR) design flow.

**B. HARD CORES:** Hard cores, by the nature of their low-level representation, offer better predictability of chip performance in terms of timing performance and area. Analog and mixed-signal logic are generally defined as a lower-level, physical description. Hence, analog IP (SerDes, PLLs, DAC, ADC, etc.) are provided to chip makers in transistor-layout format (such as GDSII.) Digital IP cores are sometimes offered in layout format, as well. Such cores, whether analog or digital, are called "hard cores" (or hard macros), because the core's application function cannot be meaningfully modified by chip designers. Transistor layouts must obey the target foundry's process design rules, and hence, hard cores delivered for one foundry's process cannot be easily ported to a different process or foundry. Merchant foundry operators (such as IBM,Fujitsu, Samsung, TI, etc.) offer a variety of hard-macro IP functions built for their own foundry process, helping to ensure customer lock-in.

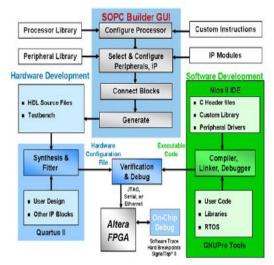

#### **III. ALTERAS HW/SW DESIGN FLOW:**

Generally the design flow starts in the Quartus II software by making a new project, subsequently, from the Quartus II the SOPC Builder tool can be accessed.In SOPC Builder the system is put together with ready intellectual property (IP)cores and/or user made IP cores. After the system is generated by the SOPC Builder tool, once again, the Quartus II software is used to add additional block s to the system, if needed. Before the system is synthesized pin assignment is made (this is also done in the Quartus II software). After synthesis and fitter operation, the Quarus II Programmer tool is used to configure the FPGA device. For software development the Nios II IDE is employed. When software debugging the GNUPro tools are used, these tools are integrated in the Nios II IDE. If real-time systemlevel debugging is required, a tool named SignalTap II logic analyzer can be utilized, thistool can be accessed from the Quartus II.

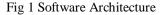

### **IV. SYSTEM GENERATION IN SOPC BUILDER**

In the project Altera's Nios II CPU is used. Nios II is a 32-bit embedded-processor architecture designed specifically for the Altera family of FPGAs. Nios II incorporates many enhancements over the original Nios architecture, making it more suitable for a wider range of embedded computing applications, from DSP to system-control.Nios II is comparable to MicroBlaze, a competing softcore CPU for the Xilinx family of FPGA. Unlike Microblaze, Nios II is licensable for standard-cell ASICs through a third-party IP provider, Synopsys Designware. Through the Designware license, designers can port Nios-based designs from an FPGA-platform to a mass production ASIC-device.Nios II is a successor to Altera's first configurable 16-bit embedded processor Nios. The Nios II processor family consists of three cores–fast (Nios II/f), economy (Nios II/e), and standard (Nios II/s) cores – each optimized for a specific price and performance range. All three cores feature a general-purpose RISC CPU architecture and share a common 32-bit instruction set architecture.

For optimizing the miniming logic usage we are using Nios II/e.It uses 600-700 logical elements and two M4ks. After instancing the CPU we are going to instance the on-chip RAM and the JATG UART. The settings of on-chip RAM can be carried out by 32 bits memory width and total size of 20kByte. The on-chip RAM is built up of M4k memory blocks. The JATG UART Read/Write FIFO is set to be constructed of registers instead of M4ks, this option is set to save M4ks, a other method to save M4k memory blocks is to reduce the Read/Write FIFO.

## V. ONCHIP EMBEDDED SYSTEM

This chapter discusses how HW/SW embedded systems are built of reusable building blocks or intellectual property (IP) within Alteras design environment. In addition software development, performance measurements and debugging is described and illustrated. The chapter starts by describing how a simple basic embedded system, consisting of a CPU, Onchip RAM and a UART, is developed. In order to utilize the systems correct function a simple application is written and ran. In Section 3.2. debugging support is added to the platform and its functions are explained. Section 3.3. describes how a high resolution timer is integrated into the system and how it is configured, with the purpose of measuring and analyzing software performance.

There is also a description on how the timer is used in applications, to measure the duration of several executions. In section 3.4. the system is extended by adding PIOs (Paralell Input Output), which in this case are used to control four LEDs with a push-button. Section 3.5. shows how the performance in the system can be enhanced, by migrating software functions to hardware. In section 3.6. the platform is further extended by integrating a RTOS kernel. The section illustrates and describes how the RTOS kernel is integrated into the system, both in HW and SW, and how it can be used in application development. In this section an external SRAM is integrated in the system.

Fig 2 System development:

The section describes how the interface to the of-chip SRAM is connected to the Avalon data bus. Subsequently a application that verifies the external SRAM is developed.

|                                            | is II TimeQuest Timing Analyzer - c:/al                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ile Edit                                   | View Netlist Constraints Repo                                                                                             | rts Script Tools Window Help                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Report                                     |                                                                                                                           | Emax Summary                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                            | TimeQuest Timing Analyzer Summary<br>Parallel Compliation                                                                 | Finax Restricted Finax Clock Name Note                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                            | Advanced I/O Timing                                                                                                       | 1 70 31 MHz 22.57 MHz altera_reserved_tck limit due to high minimum pulse width violation (tch)                                                                                                                                                                                                                                                                                                                                                   |

|                                            | Finax Surmary                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Tasks                                      | - 101 Report Hold Summary<br>- 201 Report Recovery Summary<br>- 201 Report Removed Summary<br>- 201 Report Remove Summary | *                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ▲ ] E                                      | Datableet Beport Finas Summary Beport Datasheet Device Specific Device Specific Device RSNM                               | The parel report FMAX for every clock in the design, reported as of the user specified clock periods. TMAX is only computed for paths where the<br>power and pathetization registrem or power and driven by the game clock. That is d'ifferent clocks, including generated clocks, are givened. For paths                                                                                                                                         |

|                                            | Report DDR                                                                                                                | between a clock and its investion. FMAX is computed as if the rising and falling edges are scaled along with FMAX, such that the day cycle (in terms of a percentage) is maintained. Altera recommends that you always use clock constraints and other stack reports for sign off analysis.                                                                                                                                                       |

| 150                                        | Info: High junction tem                                                                                                   | verature 1s 85 degrees C                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 151<br>152 ×<br>170<br>171<br>172<br>173 × | Warning: Node: CLOCK_50                                                                                                   | seded soc commands<br>sys besign Constraints File file not found. 'eside.doc', A synopsys besign constraints File is required by<br>was determined to be a flack but was found withmat an associated (flack assignment.<br>Thoring flack transfers have no clack uncertainty assignment, for more accurate results, apply clack unce<br>- specificate transfers have no clack uncertainty assignment. For more accurate results, apply clack unce |

| 179                                        | tob                                                                                                                       | y -parter_mane Phas Summery                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                            | Ae & History /                                                                                                            | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                            |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                            |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| r Help, pr                                 | ress F1                                                                                                                   | Ready N                                                                                                                                                                                                                                                                                                                                                                                                                                           |

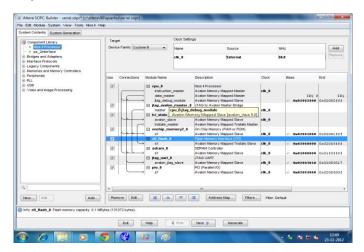

Fig 3 Performance report

| www.ijceronline.com | June   2013 | Page 21 |

|---------------------|-------------|---------|

|                     |             |         |

#### V. CONCLUSION

The capabilities of FPGAs have increased to the level where it is possible to implement a complete computer system on a single FPGA chip. The main component in such a system is a soft-core processor. The Nios soft-core processor is intended for implementation in Altera FPGAs. In this thesis project a Verilog implementation of the Nios architecture has been developed, called Nios. Performance of Nios has been investigated and compared to that of the Altera Nios. Performance analysis has shown that, although the Altera and Nios implementations are quite different, their performance is similar. Design analysis has shown that although there is little room for improvement in the current Nios organization, there is a lot of room for experimenting with different processor organizations and architectural parameters.

#### REFERANCE

- X. Wang and S.G. Ziavras, "Parallel LU Factorization of Sparse Matrices onFPGA-Based Configurable Computing Engines," Concurrency and Computation: Practice and Experience, vol. 16, no. 4, (April 2004), pp. 319-343.

- [2] Altera Corporation, "Nios Embedded Processor System Development," [OnlineDocument, Cited 2004 February 2], Available HTTP:

- [3] Xilinx, Inc., "MicroBlaze Soft Processor," [Online Document, Cited 2004 February2],vailableHTTP: [4] K. Compton and S. Hauck, "Reconfigurable Computing: A Survey of Systems andSoftware," ACM Computing Surveys, vol. 34, no. 2 (June 2002), pp. 171-210.

- [5] R. K. Gupta and Y. Zorian, "Introducing Core-Based System Design," *IEEE Design andTest of Computers*, vol. 14, no. 4 (October-December 1997), pp 15-25.

- [6] Opencores.org Web Site, [Online Document, Cited 2004 February 9]

- [7] Altera Corporation, "Excalibur Devices," [Online Document, Cited 2004 February 7], Available HTTP: [8] Xilinx, Inc., "PowerPC Embedded Processor Solution," [Online Document, Cited 2004February 7], Available HTTP:

- [9] Xilinx, Inc., "MicroBlaze Processor Reference Guide," [Online Document], 2003September, [Cited 2004 February 2], Available HTTP:

- [10] Xilinx, Inc., "PicoBlaze 8-Bit Microcontroller for Virtex-E and Spartan-II/IIE Devices,"[Online Document], 2003 February, [Cited 2004 February 2], Available HTTP:http://www.xilinx.com/bvdocs/appnotes/xapp213.pdf

- [11] V. Betz, J. Rose, and A. Marquardt, Architecture and CAD for Deep-Submicron FPGAs, Kluwer Academic Publishers: Norwell, MA, 1999.

- [12] Altera Corporation, "Stratix Device Handbook," [Online Document], 2004 January, [Cited 2004 February 3], Available HTTP:http://www.altera.com/literature/hb/stx/stratix\_handbook.pdf